In the second article in this series co-produced with Mouser Electronics, we saw how to implement embedded processors with programmable logic devices. Now, let’s see how vendors have lowered programmable logic tools‘ learning curve.

Design implementation and verification

Indeed, it’s often daunting to face a new development challenge, especially if the toolchain or process are unfamiliar, and implementing a design in a programmable logic device can appear especially so at times.

FPGA implementation tools have frequently been seen as demanding a steep learning curve and deep logic design skills if you want to end up with a solution that works.

However, programmable logic vendors have expended significant energy on this subject over the last decade. The result? More user-friendly toolchains that offer a shallower learning curve, and enable the use of higher-level languages, opening this area to a wider user base, and the field continues to evolve

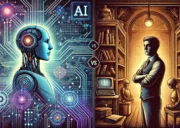

A range of tools are available for design implementation and verification that are aimed specifically at developing programmable logic solutions targeting Xilinx devices.

These tools not only support design verification and programming file creation but also allow embedded Linux operating systems and artificial intelligence and machine learning solutions to be implemented.

This technology stack opens the door to the development of solutions for both traditional FPGA and heterogeneous systems on chips that combine programmable logic with high-performance Arm processor cores.

Depending on a user’s preferred entry point, this unusual stack also enables implementation using traditional hardware design language (HDL) capture and a higher-level system-optimising compiler approach.

The design tools’ interplay can be seen in the image below. Each element of the technology stack offers a specific capability.

Vivado Design Suite

At the base of the technology stack is Vivado. Vivado allows designs to be captured using VHDL or Verilog, and the HDL design to be synthesised to the target device before placing and routing and generating the programming file.

The IP integrator at Vivado’s heart permits designers to capture designs quickly and easily using IP, whether provided by Xilinx or third parties, or custom-developed. This IP can be defined using HDL or a higher-level approach that uses Vitis HLS can be taken, enabling the development of IP blocks using C and C++.

Vivado’s focus is implementation, but a complete development ecosystem is on offer. Vivado provides several capabilities that contribute greatly to the overall development of programmable logic.

For any design, a key feature is the ability to guarantee the functional performance of the HDL prior to implementation. To verify HDL functionality, Vivado provides an HDL simulator. Depending upon the stage of implementation, the test bench can be applied against the RTL, the synthesised netlist, or against the implemented netlist with associated timing information.

Vivado is also the tool used to debug designs on the hardware, due to the support for integrated logic analysers (ILA), Virtual IO (VIO), and JTAG to AXI IP it offers. Designers are enabled to instrument the programmable logic design and observe behaviour at run time in the actual system.

Vivado’s implementation and simulation capabilities are also used by tools further up the development stack.

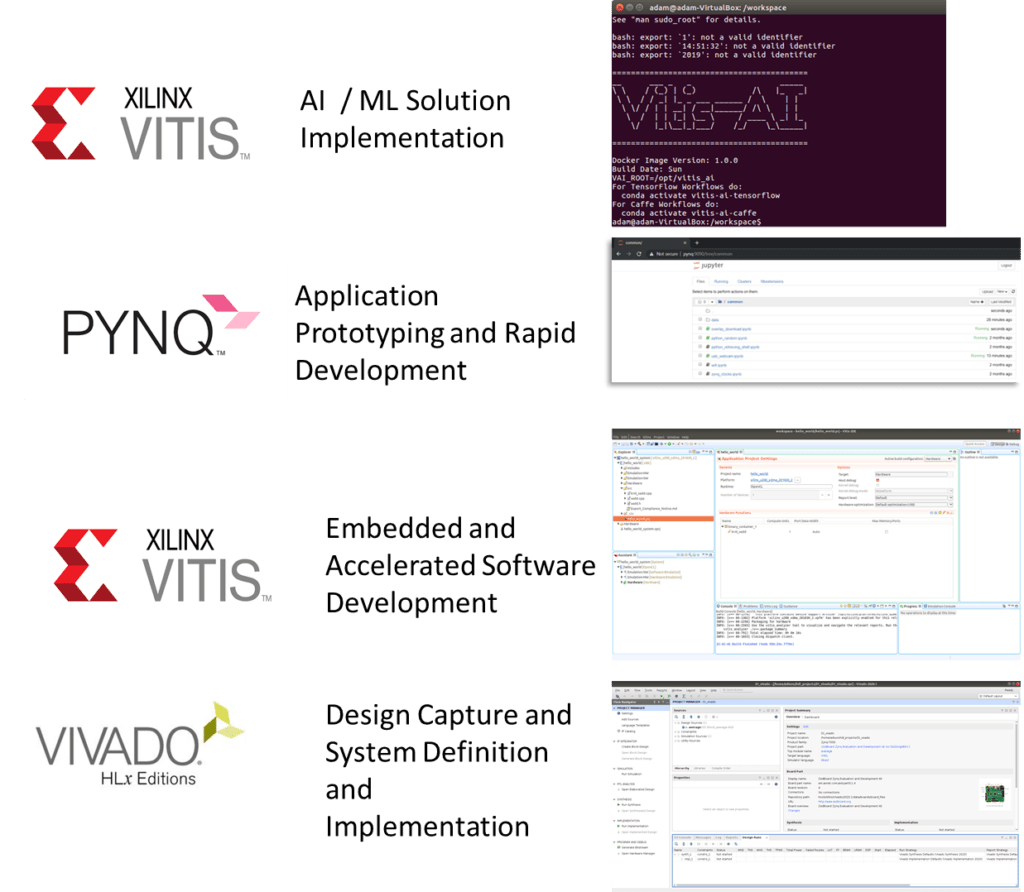

Application Software Creation

When a heterogeneous SoC or FPGA which contains a soft processor core such as a MicroBlaze enters the picture, the higher levels of the stack need to come into play to create the operating systems’ application software. The relationship between Vivado, PetaLinux and Vitis is illustrated below.

Hard and soft-core processor implementations both require operating systems to be generated and application software to be developed. Such software can be developed to run on a BareMetal, real-time operating system (FreeRTOS) or on an embedded Linux solution.

Development and debugging of the software can be achieved by using Xilinx’s Vitis unified software platform. Vitis provides two development flows – embedded and accelerated.

The embedded flow allows developers to create software solutions for any supported embedded processor. The accelerated flow enables users of Xilinx SoC and Acceleration cards to accelerate functionality from the processor system to the programmable logic.

Vitis developers can import Vivado designs to create embedded solutions when using the embedded flow. To simplify the debugging of the embedded systems, Vitis offers a complete debugger capable of supporting multi-core operation.

The software application includes operations with elements of the programmable logic design, meaning that it is also possible to cross probe and breakpoint with ILAs within the programmable logic in order to gain a greater understanding of the hardware/software interaction.

Developers who prefer an embedded Linux solution utilize the PetaLinux build tool. PetaLinux a build system rather than a Linux distribution.

Consequently, developers can configure an embedded Linux system that includes the drivers and device tree entries to work with the programmable logic design using this tool.

With a PetaLinux operating system in place for a Xilinx SoC, the developer can deploy the PYNQ framework. This enables Python and Jupiter Notebooks to be used with programmable logic. PYNQ is perfect for rapid prototyping due to the many drivers available in the Python environment to work with IP in the programmable logic, which significantly reduces the software development required.

The higher levels of the technology stack such as the Vitis acceleration capabilities and Vitis AI require a hardcore processor and embedded Linux solution or an Alveo acceleration card to access.

Acceleration

Vitis’ ability to accelerate applications into the programmable logic using OpenCL also provides an entry point for solutions that use both the processing system and the programmable logic.

To make best use of this capacity, an acceleration platform must be available to Vitis. Acceleration platforms can be created in Vivado for custom hardware and are widely available for download on many development boards.

The acceleration platform makes several system resources such as AXI interfaces, processor interrupts, and clocks available to the Vitis compiler. These resources are connected to the accelerated elements of the design in order to facilitate access from the processing system.

Vitis used the OpenCL framework to achieve this acceleration. An open industry standard developed by The Khronos Group, OpenCL enables parallel computing of heterogeneous systems. The OpenCL model includes a host – usually an x86 system, and an OpenCL device that is often called a kernel.

OpenCL provides parallel processing and application acceleration while the host manages overall application execution. An FPGA, DSP, GPU or CPU can be used to provide this parallel processing. Using OpenCL enables the source code that is running on the OpenCL device to be retargeted without any changes to the source code itself.

OpenCL provides OpenCL APIs to support this model. These can be compiled into the host application by means of standard C compilers such as GCC or G++.

OpenCL devices are developed using the OpenCL C language, derived from ISO C99. The language is not C, however, because the standard libraries are difficult to support across all the potential OpenCL devices. Consequently, each OpenCL device has a specific, vendor-provided OpenCL compiler. For Xilinx devices, this is provided by Vitis.

The following architectures are comprised of such heterogeneous systems in the Xilinx ecosystem:

- AXI interconnects link Arm processing cores and the programmable logic

- A PCIe connection links the X86 processor and Alveo acceleration cards

Both of the above architectures allow the processing element to act as the host, while – on the same silicon or in a separate device – the programmable logic is the OpenCL device.

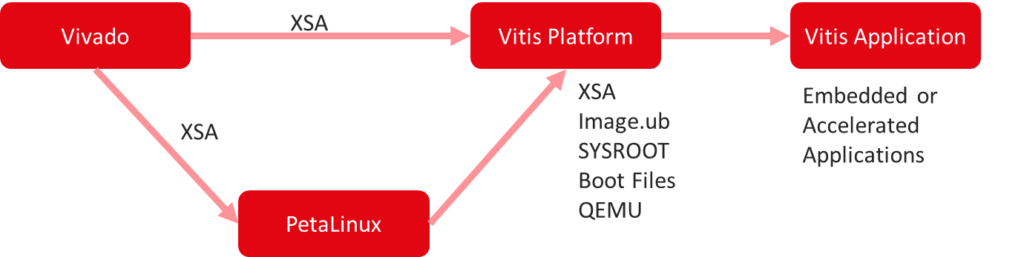

Implementation of the programmable logic design will call Vivado in the background, but this can take time to implement. Vitis also offers a range of build types for use in developing and verifying the application before generating the final bitstream.

These software emulations make it possible to correct typos and basic errors while hardware emulation leverages QEMU and co-simulation for the programmable logic design, with a resulting optimisation of performance, interfacing, and resources as shown below.

With the support of application development in mind, Vitis also provides a number of common libraries which can be accelerated into the programmable logic and several domain-specific libraries for implementation of specific applications.

The common libraries include maths, linear algebra, and DSP libraries. Computer vision, database, quantitative finance, and security all appear in the domain-specific libraries included.

Developers are given the opportunity by these libraries to leverage programmable logic performance without having to start from scratch by writing commonly-used and freely-available SW functions to be accelerated.

AI and beyond

Vitis AI builds on Vitis’ acceleration capabilities. Using Vitis, the developer can instantiate a deep learning processor unit in the programmable logic. This instantiation promotes significant acceleration for the machine learning inference applications.

Instantiating the DPU inside the programmable logic undoubtedly provides significant benefits to the developer. However, Vitis AI goes one step further by making it possible for developers to work with common machine learning and artificial intelligence frameworks such as Caffe, TensorFlow and PyTorch.

Vitis AI is not a single tool, but rather a collection of tools that compile, quantise, and optimise their machine learning applications from a floating-point implementation to a fixed-point representation suitable for implementation within the DPU.

Vitis AI additionally offers a profiler that enables system-level optimization, with the goal of aiding the development and optimisation of the DPU implementation described above,

If a developer really wants to take the hard route and start from scratch, the Xilinx Model Zoo contains several pre-optimized models.

Conclusion

Xilinx provides a range of tools that assist with the creation of FPGA and SoC solutions for use with Xilinx devices.

The tools enable design entry using HDL or OpenCL and provide solutions for embedded Linux and AI acceleration. In addition, they provide a design point for traditional FPGA designers along with software developers with the use of PYNQ, Vitis and Vitis AI.

Join us for the next instalment in this series as we explore Internal and External Interfacing- Or, if you want more technical information about the hardware you can use for your project, visit the Mouser website.